## LTC4443/LTC4443-1

#### FEATURES

- Integrated Schottky Diode

- Wide V<sub>CC</sub> Range: 6V to 9.5V

- 38V Maximum Input Supply Voltage

- Adaptive Shoot-Through Protection

- 2.4A Peak Pull-Up Current

- 5A Peak Pull-Down Current

- 8ns TG Fall Time Driving 3000pF Load

- 12ns TG Rise Time Driving 3000pF Load

- Separate Supply to Match PWM Controller

- Drives Dual N-Channel MOSFETs

- Undervoltage Lockout

- Low Profile (0.75mm) 3mm × 3mm DFN Package

#### **APPLICATIONS**

- Distributed Power Architectures

- High Density Power Modules

T, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

#### High Speed Synchronous N-Channel MOSFET Drivers

#### DESCRIPTION

The LTC<sup>®</sup>4443 is a high frequency gate driver with integrated bootstrap Schottky diode designed to drive two N-channel MOSFETs in a synchronous buck DC/DC converter topology. The powerful driver capability reduces switching losses in MOSFETs with high gate capacitance.

The LTC4443 features a separate supply for the input logic to match the signal swing of the controller IC. If the input signal is not being driven, the LTC4443 activates a shutdown mode that turns off both external MOSFETs. The input logic signal is internally level-shifted to the bootstrapped supply, which may function at up to 42V above ground. The Schottky diode required for the bootstrapped supply is integrated to simplify layout and reduce parts count.

The LTC4443 contains undervoltage lockout circuits on both the driver and logic supplies that turn off the external MOSFETs when an undervoltage condition is present. The LTC4443 and LTC4443-1 have different undervoltage lockout thresholds to accommodate a wide variety of applications. An adaptive shoot-through protection feature is also built-in to prevent power loss resulting from MOSFET cross-conduction current.

The LTC4443/LTC4443-1 are available in a tiny 3mm  $\times$  3mm DFN package.

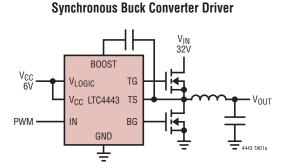

#### TYPICAL APPLICATION

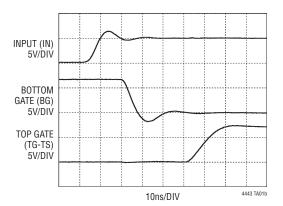

#### LTC4443 Driving 3000pF Capacitive Loads

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1) Supply Voltage

| Supply voltage                                     |

|----------------------------------------------------|

| V <sub>LOGIC</sub> –0.3V to 10V                    |

| V <sub>CC</sub> –0.3V to 10V                       |

| BOOST – TS –0.3V to 10V                            |

| BOOST Voltage –0.3V to 42V                         |

| BOOST – V <sub>CC</sub>                            |

| TS Voltage5V to 38V                                |

| TS + V <sub>CC</sub>                               |

| IN Voltage –0.3V to 10V                            |

| Driver Output TG (with Respect to TS) –0.3V to 10V |

| Driver Output BG –0.3V to 10V                      |

| Operating Temperature Range (Note 2)–40°C to 85°C  |

| Junction Temperature (Note 3) 125°C                |

| Storage Temperature Range65°C to 150°C             |

|                                                    |

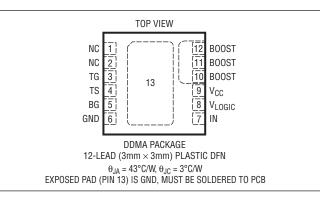

### PIN CONFIGURATION

### ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION                    | TEMPERATURE RANGE |

|------------------|--------------------|---------------|----------------------------------------|-------------------|

| LTC4443EDD#PBF   | LTC4443EDD#TRPBF   | LCXH          | 12-Lead (3mm × 3mm) Plastic DFN –40°C  |                   |

| LTC4443IDD#PBF   | LTC4443IDD#TRPBF   | LCXH          | 12-Lead (3mm × 3mm) Plastic DFN        | -40°C to 85°C     |

| LTC4443EDD-1#PBF | LTC4443EDD-1#TRPBF | LCYN          | 12-Lead (3mm $\times$ 3mm) Plastic DFN | -40°C to 85°C     |

| LTC4443IDD-1#PBF | LTC4443IDD-1#TRPBF | LCYN          | 12-Lead (3mm × 3mm) Plastic DFN        | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>CC</sub> = 7V, V<sub>TS</sub> = GND = 0V, V<sub>LOGIC</sub> = 5V, unless otherwise noted.

| SYMBOL             | PARAMETER                      | CONDITIONS                                                                                          |   | MIN          | ТҮР                 | MAX          | UNITS        |

|--------------------|--------------------------------|-----------------------------------------------------------------------------------------------------|---|--------------|---------------------|--------------|--------------|

| Logic Supply (     | V <sub>LOGIC</sub> )           |                                                                                                     |   | 1            |                     |              |              |

| V <sub>LOGIC</sub> | Operating Range                |                                                                                                     |   | 3            |                     | 9.5          | V            |

| IVLOGIC            | DC Supply Current              | IN = Floating                                                                                       |   |              | 730                 | 850          | μA           |

| UVLO               | Undervoltage Lockout Threshold | V <sub>LOGIC</sub> Rising<br>V <sub>LOGIC</sub> Falling<br>Hysteresis                               | • | 2.5<br>2.4   | 2.75<br>2.65<br>100 | 3.0<br>2.9   | V<br>V<br>mV |

| Gate Driver Su     | ipply (V <sub>CC</sub> )       |                                                                                                     | I |              |                     |              |              |

| V <sub>CC</sub>    | Operating Range                |                                                                                                     |   | 6            |                     | 9.5          | V            |

| Ivcc               | DC Supply Current              | IN = Floating                                                                                       |   |              | 600                 | 800          | μA           |

| UVLO Undervoltag   | Undervoltage Lockout Threshold | V <sub>CC</sub> Rising (LTC4443)<br>V <sub>CC</sub> Falling (LTC4443)<br>Hysteresis (LTC4443)       | • | 2.75<br>2.60 | 3.20<br>3.04<br>160 | 3.65<br>3.50 | V<br>V<br>mV |

|                    |                                | V <sub>CC</sub> Rising (LTC4443-1)<br>V <sub>CC</sub> Falling (LTC4443-1)<br>Hysteresis (LTC4443-1) | • | 5.6<br>4.7   | 6.2<br>5.3<br>850   | 6.7<br>5.8   | V<br>V<br>mV |

|                    |                                |                                                                                                     |   |              |                     |              | 4443fa       |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>CC</sub> = 7V, V<sub>TS</sub> = GND = 0V, V<sub>LOGIC</sub> = 5V, unless otherwise noted.

| SYMBOL               | PARAMETER                                          | CONDITIONS                                                        |   | MIN        | ТҮР          | MAX        | UNITS    |

|----------------------|----------------------------------------------------|-------------------------------------------------------------------|---|------------|--------------|------------|----------|

| VD                   | Schottky Diode Forward Voltage                     | I <sub>D</sub> = 10mA<br>I <sub>D</sub> = 100mA                   |   |            | 0.38<br>0.48 |            | V<br>V   |

| Input Signal (I      | N)                                                 |                                                                   |   |            |              |            |          |

| V <sub>IH(TG)</sub>  | TG Turn-On Input Threshold                         | $V_{LOGIC} \ge 5V$ , IN Rising $V_{LOGIC} = 3.3V$ , IN Rising     | • | 3.0<br>1.9 | 3.5<br>2.2   | 4.0<br>2.6 | V<br>V   |

| V <sub>IL(TG)</sub>  | TG Turn-Off Input Threshold                        | $V_{LOGIC} \ge 5V$ , IN Falling $V_{LOGIC} = 3.3V$ , IN Falling   |   |            | 3.25<br>2.09 |            | V<br>V   |

| V <sub>IH(BG)</sub>  | BG Turn-On Input Threshold                         | $V_{LOGIC} \ge 5V$ , IN Falling $V_{LOGIC} = 3.3V$ , IN Falling   | • | 0.8<br>0.8 | 1.25<br>1.10 | 1.6<br>1.4 | V<br>V   |

| V <sub>IL(BG)</sub>  | BG Turn-Off Input Theshold                         | $V_{LOGIC} \ge 5V$ , IN Rising $V_{LOGIC} = 3.3V$ , IN Rising     |   |            | 1.50<br>1.21 |            | V<br>V   |

| I <sub>IN(SD)</sub>  | Maximum Current Into or Out of IN in Shutdown Mode | $V_{LOGIC} \ge 5V$ , IN Floating $V_{LOGIC} = 3.3V$ , IN Floating |   | 200<br>100 | 300<br>150   |            | μA<br>μA |

| High Side Gate       | e Driver Output (TG)                               |                                                                   |   |            |              |            |          |

| V <sub>OH(TG)</sub>  | TG High Output Voltage                             | $I_{TG} = -10 \text{mA}, V_{OH(TG)} = V_{BOOST} - V_{TG}$         |   |            | 0.7          |            | V        |

| V <sub>OL(TG)</sub>  | TG Low Output Voltage                              | $I_{TG}$ = 100mA, $V_{OL(TG)}$ = $V_{TG} - V_{TS}$                |   |            | 100          |            | mV       |

| I <sub>PU(TG)</sub>  | TG Peak Pull-Up Current                            |                                                                   |   | 1.5        | 2.4          |            | A        |

| I <sub>PD(TG)</sub>  | TG Peak Pull-Down Current                          |                                                                   |   | 1.5        | 2.4          |            | A        |

| Low Side Gate        | e Driver Output (BG)                               |                                                                   |   |            |              |            |          |

| V <sub>OH(BG)</sub>  | BG High Output Voltage                             | $I_{BG} = -10 \text{mA}, V_{OH(BG)} = V_{CC} - V_{BG}$            |   |            | 0.7          |            | V        |

| V <sub>OL(BG)</sub>  | BG Low Output Voltage                              | I <sub>BG</sub> = 100mA                                           |   |            | 100          |            | mV       |

| I <sub>PU(BG)</sub>  | BG Peak Pull-Up Current                            |                                                                   |   | 1.4        | 2.4          |            | A        |

| I <sub>PD(BG)</sub>  | BG Peak Pull-Down Current                          |                                                                   |   | 3.5        | 5.0          |            | A        |

| Switching Tim        | e                                                  |                                                                   |   |            |              |            |          |

| t <sub>PLH(TG)</sub> | BG Low to TG High Propagation Delay                |                                                                   |   |            | 20           |            | ns       |

| t <sub>PHL(TG)</sub> | IN Low to TG Low Propagation Delay                 |                                                                   |   |            | 12           |            | ns       |

| t <sub>PLH(BG)</sub> | TG Low to BG High Propagation Delay                |                                                                   |   |            | 20           |            | ns       |

| t <sub>PHL(BG)</sub> | IN High to BG Low Propagation Delay                |                                                                   |   |            | 12           |            | ns       |

| t <sub>r(TG)</sub>   | TG Output Rise Time                                | 10% – 90%, C <sub>L</sub> = 3nF                                   |   |            | 12           |            | ns       |

| t <sub>f(TG)</sub>   | TG Output Fall Time                                | 10% - 90%, C <sub>L</sub> = 3nF                                   |   |            | 8            |            | ns       |

| t <sub>r(BG)</sub>   | BG Output Rise Time                                | 10% - 90%, C <sub>L</sub> = 3nF                                   |   |            | 12           |            | ns       |

| t <sub>f(BG)</sub>   | BG Output Fall Time                                | 10% - 90%, C <sub>L</sub> = 3nF                                   |   |            | 5            |            | ns       |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC4443I/LTC4443I-1 are guaranteed to meet specifications from -40°C to 85°C. The LTC4443E/LTC4443E-1 are guaranteed to meet specifications from 0°C to 85°C with specifications over the -40°C to 85°C operating temperature range assured by design, characterization and correlation with statistical process controls.

$T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$ according to the following formula:

$$T_J = T_A + (PD \bullet 43^{\circ}C/W)$$

Note 3: This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

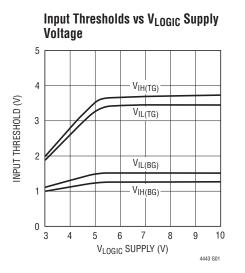

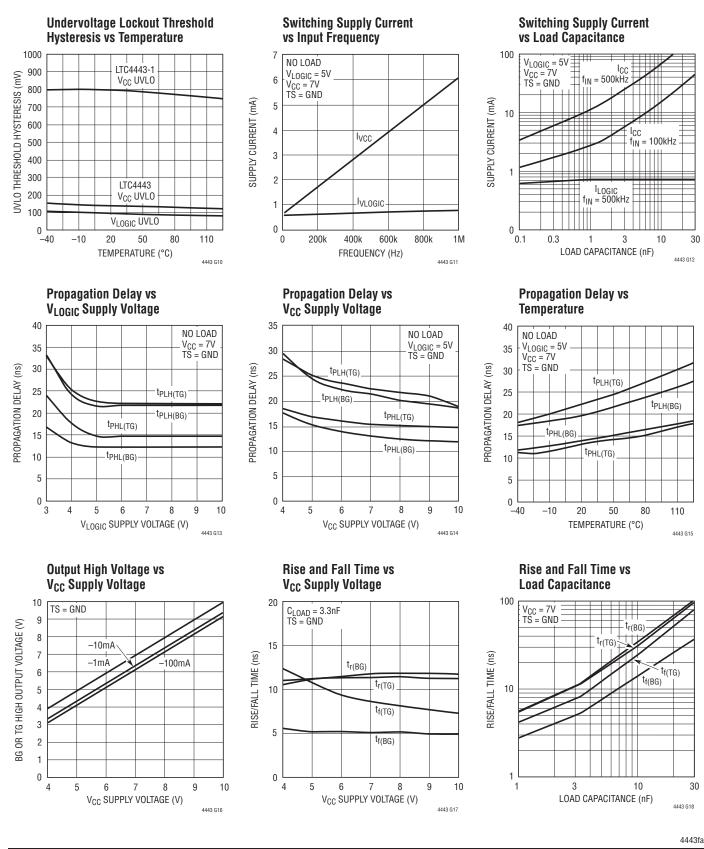

### TYPICAL PERFORMANCE CHARACTERISTICS

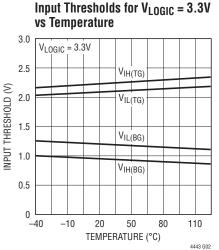

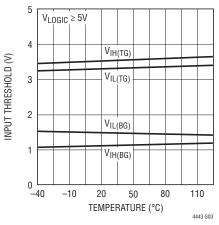

Input Thresholds for  $V_{LOGIC} \geq 5V$  vs Temperature

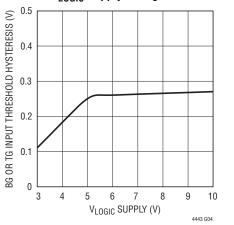

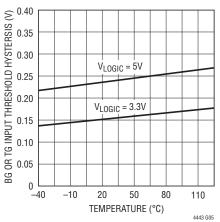

BG or TG Input Threshold Hysteresis vs V<sub>LOGIC</sub> Supply Voltage

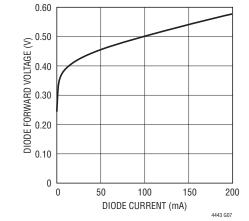

Schottky Diode Forward Voltage vs Diode Current

BG or TG Input Threshold Hysteresis vs Temperature

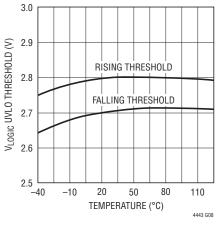

V<sub>LOGIC</sub> Undervoltage Lockout Thresholds vs Temperature

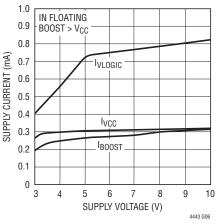

Quiescent Supply Current vs Supply Voltage

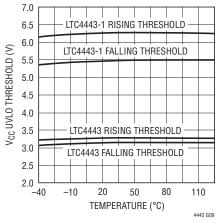

V<sub>CC</sub> Undervoltage Lockout Thresholds vs Temperature

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

5

#### PIN FUNCTIONS

**TG (Pin 3):** High Side Gate Driver Output (Top Gate). This pin swings between TS and BOOST.

**TS (Pin 4):** High Side MOSFET Source Connection (Top Source).

**BG (Pin 5):** Low Side Gate Driver Output (Bottom Gate). This pin swings between  $V_{CC}$  and GND.

#### GND (Pin 6): Chip Ground.

**IN (Pin 7):** Input Signal. Input referenced to an internal supply powered by  $V_{LOGIC}$  (Pin 8) and referenced to GND (Pin 6). If this pin is floating, an internal resistive divider triggers a shutdown mode in which both BG (Pin 5) and TG (Pin 3) are pulled low. Trace capacitance on this pin should be minimized to keep the shutdown time low.

$V_{LOGIC}$  (Pin 8): Logic Supply. This pin powers the input buffer and logic. Connect this pin to the power supply of the controller that is driving IN (Pin 7) to match input thresholds or to V<sub>CC</sub> (Pin 9) to simplify PCB routing.

$V_{CC}$  (Pin 9): Output Driver Supply. This pin powers the low side gate driver output directly and the high side gate driver output through an internal Schottky diode connected between this pin and BOOST. A low ESR ceramic bypass capacitor should be tied between this pin and GND (Pin 6).

**BOOST (Pins 10, 11, 12):** High Side Bootstrapped Supply. An external capacitor should be tied between these pins and TS (Pin 4). An internal Schottky diode is connected between  $V_{CC}$  (Pin 9) and these pins. Voltage swing at these pins is from  $V_{CC} - V_D$  to  $V_{IN} + V_{CC} - V_D$ , where  $V_D$  is the forward voltage drop of the bootstrap diode.

**Exposed Pad (Pin 13):** Ground. The Exposed Pad must be soldered to PCB ground for optimal electrical and thermal performance.

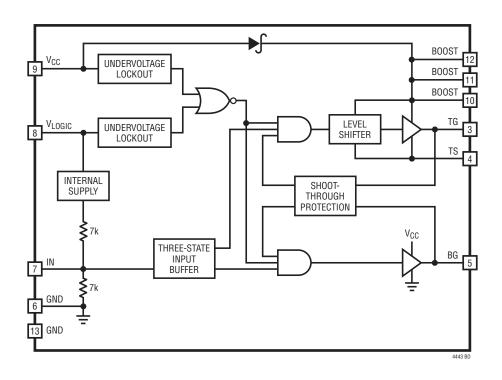

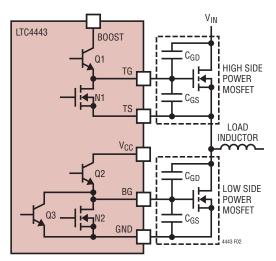

### **BLOCK DIAGRAM**

4443fa

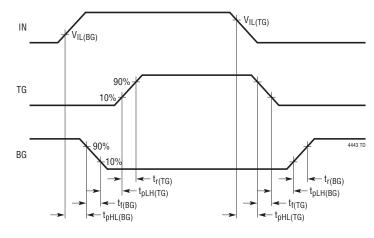

#### TIMING DIAGRAM

### OPERATION

#### Overview

The LTC4443 receives a ground-referenced, low voltage digital input signal to drive two N-channel power MOSFETs in a synchronous buck power supply configuration. The gate of the low side MOSFET is driven either to  $V_{CC}$  or GND, depending on the state of the input. Similarly, the gate of the high side MOSFET is driven to either BOOST or TS by a supply bootstrapped off of the switch node (TS).

#### **Input Stage**

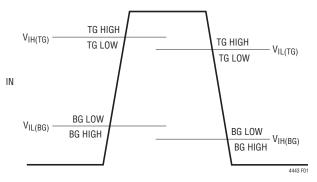

The LTC4443 employs a unique three-state input stage with transition thresholds that are proportional to the V<sub>LOGIC</sub> supply. The V<sub>LOGIC</sub> supply can be tied to the controller IC's power supply so that the input thresholds will match those of the controller's output signal. Alternatively, V<sub>LOGIC</sub> can be tied to V<sub>CC</sub> to simplify routing. An internal voltage regulator in the LTC4443 limits the input threshold values for V<sub>LOGIC</sub> supply voltages greater than 5V.

The relationship between the transition thresholds and the three input states of the LTC4443 is illustrated in Figure 1. When the voltage on IN is greater than the threshold V<sub>IH(TG)</sub>, TG is pulled up to BOOST, turning the high side MOSFET on. This MOSFET will stay on until IN falls below V<sub>IL(TG)</sub>. Similarly, when IN is less than V<sub>IH(BG)</sub>, BG is pulled up to V<sub>CC</sub>, turning the low side (synchronous) MOSFET on. BG will stay high until IN increases above the threshold V<sub>IL(BG)</sub>.

The thresholds are positioned to allow for a region in which both BG and TG are low. An internal resistive divider will pull IN into this region if the signal driving the IN pin goes into a high impedance state.

One application of this three-state input is to keep both of the power MOSFETs off while an undervoltage condition exists on the controller IC power supply. This can be accomplished by driving the IN pin with a logic buffer that has an enable pin. With the enable pin of the buffer tied to the power good pin of the controller IC, the logic buffer output will remain in a high impedance state until the controller confirms that its supply is not in an undervoltage state. The three-state input of the LTC4443 will therefore pull IN into the region where TG and BG are low until the controller has enough voltage to operate predictably.

## OPERATION

The hysteresis between the corresponding  $V_{IH}$  and  $V_{IL}$  voltage levels eliminates false triggering due to noise during switch transitions; however, care should be taken to keep noise from coupling into the IN pin, particularly in high frequency, high voltage applications.

#### Undervoltage Lockout

The LTC4443 contains undervoltage lockout detectors that monitor both the V<sub>CC</sub> and V<sub>LOGIC</sub> supplies. When V<sub>CC</sub> falls below 3.04V or V<sub>LOGIC</sub> falls below 2.65V, the output pins BG and TG are pulled to GND and TS, respectively. This turns off both of the external MOSFETs. When V<sub>CC</sub> and V<sub>LOGIC</sub> have adequate supply voltage for the LTC4443 to operate reliably, normal operation will resume.

#### Adaptive Shoot-Through Protection

Internal adaptive shoot-through protection circuitry monitors the voltages on the external MOSFETs to ensure that they do not conduct simultaneously. The LTC4443 does not allow the bottom MOSFET to turn on until the gate-source voltage on the top MOSFET is sufficiently low, and vice-versa. This feature improves efficiency by eliminating cross-conduction current from flowing from the V<sub>IN</sub> supply through the MOSFETs to ground during a switch transition.

#### Output Stage

A simplified version of the LTC4443's output stage is shown in Figure 2. The pull-up device on both the BG and TG outputs is an NPN bipolar junction transistor (Q1 and Q2). The BG and TG outputs are pulled up to within an NPN V<sub>BE</sub> (~0.7V) of their positive rails (V<sub>CC</sub> and BOOST, respectively). Both BG and TG have N-channel MOSFET pull-down devices (N1 and N2) which pull BG and TG down to their negative rails, GND and TS. An additional NPN bipolar junction transistor (Q3) is present on BG to increase its pull-down drive current capacity. The large voltage swing of the BG and TG output pins is important in driving external power MOSFETs, whose  $R_{DS(ON)}$  is inversely proportional to its gate overdrive voltage (V<sub>GS</sub> – V<sub>TH</sub>).

Figure 2. Capacitance Seen by BG and TG During Switching

#### **Rise/Fall Time**

Since the power MOSFET generally accounts for the majority of power loss in a converter, it is important to quickly turn it on and off, thereby minimizing the transition time and power loss. The LTC4443's peak pull-up current of 2.4A for both BG and TG (Q1 and Q2) produces a rapid turn-on transition for the MOSFETs. This high current is capable of driving a 3nF load with a 12ns rise time.

It is also important to turn the power MOSFETs off quickly to minimize power loss due to transition time: however. an additional benefit of a strong pull-down on the driver outputs is the prevention of cross-conduction current. For example, when BG turns the low side power MOSFET off and TG turns the high side power MOSFET on, the voltage on the TS pin will rise to V<sub>IN</sub> very rapidly. This high frequency positive voltage transient will couple through the C<sub>GD</sub> capacitance of the low side power MOSFET to the BG pin. If the BG pin is not held down sufficiently, the voltage on the BG pin will rise above the threshold voltage of the low side power MOSFET, momentarily turning it back on. As a result, both the high side and low side MOSFETs will be conducting, which will cause significant cross-conduction current to flow through the MOSFETs from V<sub>IN</sub> to ground, thereby introducing substantial power loss. A similar effect occurs on TG due to the  $C_{GS}$  and  $C_{GD}$ capacitances of the high side MOSFET.

## OPERATION

The LTC4443's powerful parallel combination of the N-channel MOSFET (N2) and NPN (Q3) on the BG pull-down generates a phenomenal 5ns fall time on BG while driving a 3nF load. Similarly, the  $1\Omega$  pull-down MOSFET (N1) on

### **APPLICATIONS INFORMATION**

#### **Power Dissipation**

To ensure proper operation and long-term reliability, the LTC4443 must not operate beyond its maximum temperature rating. Package junction temperature can be calculated by:

$\mathsf{T}_\mathsf{J} = \mathsf{T}_\mathsf{A} + (\mathsf{P}_\mathsf{D})(\boldsymbol{\theta}_\mathsf{J}_\mathsf{A})$

where:

T<sub>J</sub> = Junction temperature

T<sub>A</sub> = Ambient temperature

P<sub>D</sub> = Power dissipation

$\theta_{JA}$  = Junction-to-ambient thermal resistance

Power dissipation consists of standby, switching and capacitive load power losses:

$\mathsf{P}_\mathsf{D} = \mathsf{P}_\mathsf{DC} + \mathsf{P}_\mathsf{AC} + \mathsf{P}_\mathsf{QG}$

where:

P<sub>DC</sub> = Quiescent power loss

$P_{AC}$  = Internal switching loss at input frequency  $f_{IN}$

$P_{QG}$  = Loss due turning on and off the external

MOSFET with gate charge  $Q_G$  at frequency  $f_{IN}$

The LTC4443 consumes very little quiescent current. The DC power loss at  $V_{LOGIC} = 5V$  and  $V_{CC} = V_{BOOST} - TS = 7V$  is only (730µA)(5V) + (600µA)(7V) = 7.85mW.

At a particular switching frequency, the internal power loss increases due to both AC currents required to charge and discharge internal nodal capacitances and cross-conduction currents in the internal logic gates. The sum of the quiescent current and internal switching current with no TG results in a rapid 8ns fall time with a 3nF load. These powerful pull-down devices minimize the power loss associated with MOSFET turn-off time and cross-conduction current.

load are shown in the Typical Performance Characteristics plot of Switching Supply Current vs Input Frequency.

The gate charge losses are primarily due to the large AC currents required to charge and discharge the capacitance of the external MOSFETs during switching. For identical pure capacitive loads  $C_{LOAD}$  on TG and BG at switching frequency fin, the load losses would be:

$P_{CLOAD} = (C_{LOAD})(f_{IN})[(V_{BOOST} - TS)^{2} + (V_{CC})^{2}]$

In a typical synchronous buck configuration,  $V_{BOOST}-TS$  is equal to  $V_{CC}-V_D$ , where  $V_D$  is the forward voltage drop of the internal Schottky diode between  $V_{CC}$  and BOOST. If this drop is small relative to  $V_{CC}$ , the load losses can be approximated as:

$P_{CLOAD} \approx 2(C_{LOAD})(f_{IN})(V_{CC})^2$

Unlike a pure capacitive load, a power MOSFET's gate capacitance seen by the driver output varies with its  $V_{GS}$  voltage level during switching. A MOSFET's capacitive load power dissipation can be calculated using its gate charge,  $Q_G$ . The  $Q_G$  value corresponding to the MOSFET's  $V_{GS}$  value ( $V_{CC}$  in this case) can be readily obtained from the manufacturer's QG vs  $V_{GS}$  curves. For identical MOSFETs on TG and BG:

$\mathsf{P}_{QG}\approx 2(\mathsf{V}_{CC})(\mathsf{Q}_G)(\mathsf{f}_{\mathsf{IN}})$

To avoid damaging junction temperatures due to power dissipation, the LTC4443 includes a temperature monitor that will pull BG and TG low if the junction temperature exceeds 160°C. Normal operation will resume when the junction temperature cools to less than 135°C.

### **APPLICATIONS INFORMATION**

#### **Bypassing and Grounding**

The LTC4443 requires proper bypassing on the V<sub>LOGIC</sub>, V<sub>CC</sub> and V<sub>BOOST</sub> – TS supplies due to its high speed switching (nanoseconds) and large AC currents (Amperes). Careless component placement and PCB trace routing may cause excessive ringing and undershoot/overshoot.

To obtain the optimum performance from the LTC4443:

- A. Mount the bypass capacitors as close as possible between the  $V_{LOGIC}$  and GND pins, the  $V_{CC}$  and GND pins, and the BOOST and TS pins. The leads should be shortened as much as possible to reduce lead inductance.

- B. Use a low inductance, low impedance ground plane to reduce any ground drop and stray capacitance. Remember that the LTC4443 switches greater than

5A peak currents and any significant ground drop will degrade signal integrity.

- C. Plan the power/ground routing carefully. Know where the large load switching current is coming from and going to. Maintain separate ground return paths for the input pin and the output power stage.

- D. Keep the copper trace between the driver output pin and the load short and wide.

- E. Be sure to solder the Exposed Pad on the back side of the LTC4443 packages to the board. Correctly soldered to a double-sided copper board, the LTC4443 has a thermal resistance of approximately 43°C/W. Failure to make good thermal contact between the exposed back side and the copper board will result in thermal resistances far greater.

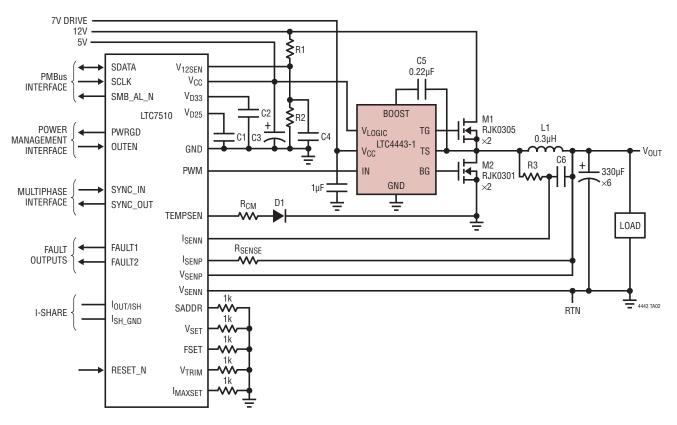

### TYPICAL APPLICATION

LTC7510/LTC4443-1 12V to 1.5V/30A Digital Step-Down DC/DC Converter with PMBus Serial Interface

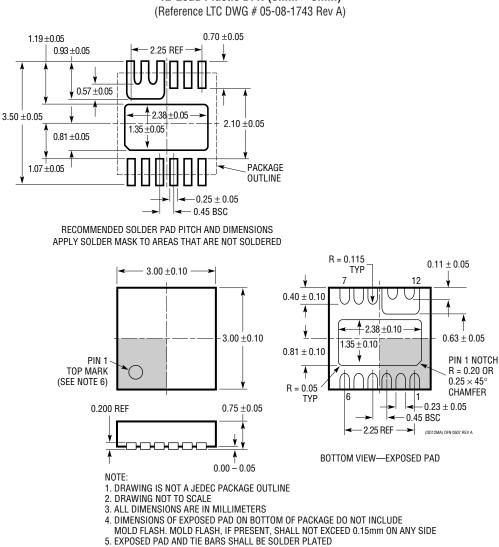

#### PACKAGE DESCRIPTION

**DDMA Package** 12-Lead Plastic DFN (3mm × 3mm)

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

### **RELATED PARTS**

| PART NUMBER       | DESCRIPTION                                         | COMMENTS                                                                                                                |

|-------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| LT®1161           | Quad Protected High Side MOSFET Driver              | 8V to 48V Supply Range, $t_{ON}$ = 200µs, $t_{OFF}$ = 28µs                                                              |

| LTC1693 Family    | High Speed Single/Dual N-Channel MOSFET Drivers     | 1.5A Peak Output Current, $4.5V \le V_{IN} \le 13.2V$                                                                   |

| LTC4440           | High Speed, High Voltage High Side Gate Driver      | High Side Source Up to 100V, $8V \le V_{CC} \le 15V$                                                                    |

| LTC4440-5         | High Speed, High Voltage High Side Gate Driver      | High Side Source Up to 80V, $4V \le V_{CC} \le 15V$                                                                     |

| LTC4441           | 6A MOSFET Driver                                    | 6A Peak Output Current, Adjustable Gate Drive from 5V to 8V, $5V \leq V_{IN} \leq 25V$                                  |

| LTC4442/LTC4442-1 | High Speed Synchronous N-Channel MOSFET Driver      | 5A Peak Output Current, Three-State Input, 38V Maximum Input Supply Voltage, 6V $\leq$ V_{CC} $\leq$ 9.5V, MS8E Package |

| LTC4444           | High Voltage Synchronous N-Channel MOSFET Driver    | High Side Source Up to 100V, 3A Peak Output Current, $7.2V \leq V_{CC} \leq 13.5V$                                      |

| LTC4445/LTC4445-1 | Dual High Speed Synchronous N-Channel MOSFET Driver | Two Independent Drivers, Internal Schottky Diodes, 38V Maximum Input Supply Voltage, $6V \le V_{CC} \le 9.5V$ ,         |

| LTC4447           | High Speed Synchronous N-Channel MOSFET Driver      | 4.5A Peak Output Current, Rail-to-Rail Drivers, 38V Maximum Input Supply Voltage, 4V $\leq V_{CC} \leq 6.5V$            |

| LTC7510           | Digital DC/DC Controller with PMBus Interface       | Digital Controller, PMBus Serial Interface, 150kHz to 2MHz<br>Switching Frequency                                       |